FPGA在物聯(lián)網(wǎng)和邊緣計(jì)算中的機(jī)會(huì)與挑戰(zhàn)

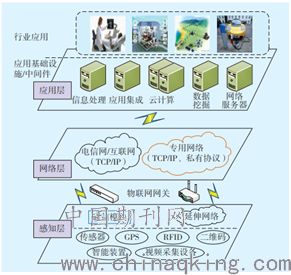

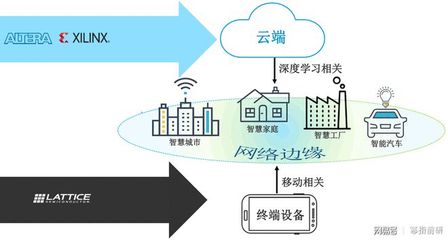

隨著物聯(lián)網(wǎng)(IoT)技術(shù)的飛速發(fā)展和邊緣計(jì)算的興起,現(xiàn)場(chǎng)可編程門陣列(FPGA)憑借其獨(dú)特的硬件可重構(gòu)性、低延遲和高能效比,正成為連接物理世界與數(shù)字智能的關(guān)鍵橋梁。本文旨在探討FPGA在物聯(lián)網(wǎng)技術(shù)服務(wù)體系中所面臨的重要機(jī)遇與核心挑戰(zhàn),并分析其未來演進(jìn)路徑。

一、 FPGA在物聯(lián)網(wǎng)與邊緣計(jì)算中的核心機(jī)會(huì)

- 實(shí)時(shí)性與低延遲處理:物聯(lián)網(wǎng)邊緣節(jié)點(diǎn)需要對(duì)傳感器數(shù)據(jù)(如視覺、振動(dòng)、聲音)進(jìn)行即時(shí)分析與響應(yīng)。FPGA的并行處理架構(gòu)能夠?qū)崿F(xiàn)硬件級(jí)的數(shù)據(jù)流處理,顯著降低從數(shù)據(jù)采集到?jīng)Q策執(zhí)行的延遲,滿足工業(yè)控制、自動(dòng)駕駛、智能安防等場(chǎng)景對(duì)實(shí)時(shí)性的苛刻要求。

- 能效比優(yōu)化:海量的物聯(lián)網(wǎng)設(shè)備通常部署在供電受限或電池驅(qū)動(dòng)的環(huán)境中。FPGA可以通過定制化硬件邏輯,僅實(shí)現(xiàn)特定算法所需的精確電路,避免了通用處理器(如CPU)的指令開銷與功耗浪費(fèi),從而在單位功耗下提供更高的計(jì)算性能,極大延長(zhǎng)設(shè)備續(xù)航。

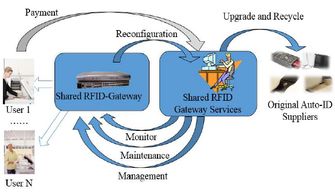

- 靈活性與可重構(gòu)性:物聯(lián)網(wǎng)應(yīng)用場(chǎng)景碎片化嚴(yán)重,協(xié)議與算法迭代迅速。FPGA無需流片即可在部署后重新配置硬件功能,允許開發(fā)者通過遠(yuǎn)程更新,快速適配新的通信協(xié)議(如5G、LoRa)、安全算法或機(jī)器學(xué)習(xí)模型,為終端設(shè)備提供了面向未來的“硬件可進(jìn)化”能力。

- 增強(qiáng)邊緣智能與數(shù)據(jù)安全:FPGA可在邊緣側(cè)高效運(yùn)行輕量化AI推理模型(如CNN、RNN),實(shí)現(xiàn)數(shù)據(jù)在源頭處的智能過濾與預(yù)處理,減少云端傳輸負(fù)擔(dān)與帶寬成本。其硬件隔離特性有助于構(gòu)建可信執(zhí)行環(huán)境(TEE),將密鑰管理、加密運(yùn)算等安全模塊固化于硬件中,提升整體系統(tǒng)的抗攻擊能力。

二、 FPGA規(guī)模化應(yīng)用面臨的主要挑戰(zhàn)

- 開發(fā)門檻與生態(tài)瓶頸:傳統(tǒng)FPGA設(shè)計(jì)依賴硬件描述語言(如Verilog、VHDL),開發(fā)周期長(zhǎng)、調(diào)試復(fù)雜,需要兼具軟硬件知識(shí)的復(fù)合型人才。盡管高層次綜合(HLS)等工具在簡(jiǎn)化開發(fā),但相比成熟的CPU/GPU軟件生態(tài),其開發(fā)工具鏈、算法庫及社區(qū)支持仍顯不足,制約了在廣大物聯(lián)網(wǎng)開發(fā)者中的普及。

- 成本與規(guī)模化部署難題:盡管單位性能功耗比優(yōu)異,但中高端FPGA芯片的單價(jià)仍顯著高于通用微控制器(MCU)或?qū)S眉呻娐罚ˋSIC)。對(duì)于需要海量部署的低成本物聯(lián)網(wǎng)終端(如消費(fèi)級(jí)傳感器),F(xiàn)PGA的經(jīng)濟(jì)性優(yōu)勢(shì)尚不突出。如何平衡性能、靈活性與成本,是FPGA方案商需要解決的關(guān)鍵問題。

- 動(dòng)態(tài)可重構(gòu)的管理復(fù)雜性:雖然可重構(gòu)性是優(yōu)勢(shì),但在實(shí)際物聯(lián)網(wǎng)系統(tǒng)中,對(duì)分布在各地的設(shè)備進(jìn)行安全、可靠、大規(guī)模的硬件功能遠(yuǎn)程更新,涉及版本管理、回滾機(jī)制、網(wǎng)絡(luò)安全等一系列復(fù)雜運(yùn)維挑戰(zhàn),對(duì)設(shè)備管理平臺(tái)提出了更高要求。

- 標(biāo)準(zhǔn)與互操作性的缺失:物聯(lián)網(wǎng)領(lǐng)域協(xié)議與接口標(biāo)準(zhǔn)眾多,F(xiàn)PGA作為硬件加速單元,需要與主處理器、傳感器、網(wǎng)絡(luò)模塊及其他加速器高效協(xié)同。目前缺乏統(tǒng)一的硬件抽象層或標(biāo)準(zhǔn)化接口,增加了系統(tǒng)集成難度,影響了不同供應(yīng)商組件間的互操作性。

三、 未來展望與建議

面向FPGA在物聯(lián)網(wǎng)與邊緣計(jì)算中的潛力釋放,有賴于技術(shù)、生態(tài)與商業(yè)模式的協(xié)同創(chuàng)新:

- 技術(shù)層:推動(dòng)開發(fā)工具進(jìn)一步軟件化、智能化,降低編程門檻;發(fā)展異構(gòu)計(jì)算架構(gòu),將FPGA與CPU、GPU、NPU等集成于同一平臺(tái),實(shí)現(xiàn)任務(wù)的高效協(xié)同調(diào)度。

- 生態(tài)層:構(gòu)建開源硬件設(shè)計(jì)庫與IP市場(chǎng),鼓勵(lì)算法廠商提供經(jīng)過優(yōu)化的FPGA版內(nèi)核;加強(qiáng)與云計(jì)算服務(wù)商的合作,提供從邊緣到云的“FPGA即服務(wù)”無縫體驗(yàn)。

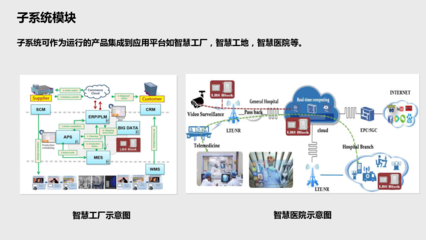

- 應(yīng)用層:聚焦對(duì)實(shí)時(shí)性、能效、安全性要求極高的垂直領(lǐng)域(如工業(yè)互聯(lián)網(wǎng)、智能醫(yī)療、車聯(lián)網(wǎng))進(jìn)行深度優(yōu)化,打造標(biāo)桿解決方案,再逐步向更廣闊市場(chǎng)輻射。

FPGA以其獨(dú)特的硬件靈活性,為物聯(lián)網(wǎng)與邊緣計(jì)算帶來了處理實(shí)時(shí)數(shù)據(jù)、實(shí)現(xiàn)高效智能與保障安全隱私的新范式。盡管面臨開發(fā)復(fù)雜性、成本與生態(tài)成熟度等挑戰(zhàn),但隨著技術(shù)工具鏈的完善、異構(gòu)計(jì)算模式的普及以及邊緣AI需求的爆發(fā),F(xiàn)PGA有望在構(gòu)建下一代智能、自適應(yīng)、高可靠的物聯(lián)網(wǎng)技術(shù)服務(wù)體系中,扮演愈發(fā)核心的角色。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.zhongjingshiye.com.cn/product/76.html

更新時(shí)間:2026-02-23 04:29:41